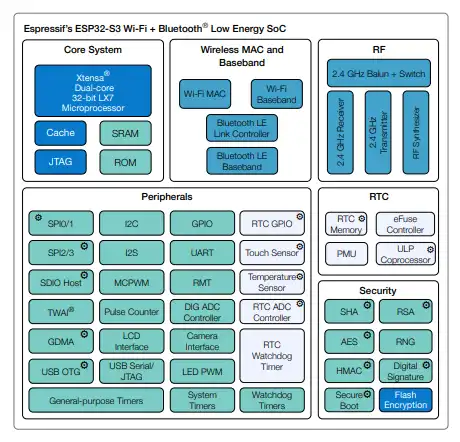

The ESP32-S3 SoC is the new flagship from manufacturer Espressif Systems, coming to solidify the dominance of the ESP32 family in the IoT microcontroller arena.

The ESP32-S3 offers an unprecedented level of power and versatility, providing a wide range of features and functionalities that make it an ideal choice for IoT projects, wearable devices, and embedded applications.

The ESP32-S3 is equipped with a dual-core Xtensa LX7 RISC-V processor capable of reaching a clock speed of up to 240 MHz. That means we get back the dual-core we had in the original ESP32, which was missing in the S2.

Regarding memory, the ESP32-S3 has 384 KB ROM, 512 KB SRAM. That is, a memory capacity much higher than the S2, and similar to what we had in the original ESP32.

Regarding wireless connectivity, the ESP32-S3 retains Wi-Fi connectivity, which as we know is one of the standout features of all ESP32s. But it incorporates improvements such as support for the new Wi-Fi 802.11b/g/n/ac standards.

Furthermore, the ESP32-S3 includes Bluetooth 5.0, a feature we had lost in the S2. Very interesting for integration with other IoT devices and expands the possibilities for application development.

In terms of connectivity, we have the huge number of interfaces typically found in the ESP32 family. Among them, it features 45x GPIO, UART, SPI, I2C, I2S, and PWM (check the table at the end of the article because the list is huge).

On the other hand, the ESP32-S3 SoC includes several power-saving modes, allowing for energy consumption optimization based on application requirements. It also features a dedicated Ultra Low Power (ULP) co-processor (which can handle specific low-power tasks).

Finally, the S3 maintains the same security features found in the S2, such as a hardware random number generator (RNG), support for AES and RSA cryptography, and a dedicated security unit (HSM) that protects keys and cryptographic operations.

{ “CPU and Memory”: [ { “label”: “CPU”, “value”: “Xtensa® dual-core 32-bit LX7 microprocessor, up to 240 MHz” }, { “label”: “Memory”, “value”: “384 KB ROM, 512 KB SRAM, 16 KB RTC SRAM” }, { “label”: “Memory Interfaces”, “value”: [“128-bit data bus and SIMD commands”, “SPI, Dual SPI, Quad SPI, Octal SPI, QPI and OP”] } ], “Peripherals”: [ { “label”: “GPIO”, “value”: “45 × programmable GPIOs” }, { “label”: “ADC”, “value”: “2 × 12-bit SAR ADCs, up to 20 channels” }, { “label”: “Interfaces”, “value”: “3 UART, 4 SPI, 2 I2C, 2 I2S, 1 RMT TX/RX” }, { “label”: “Multimedia Interfaces”, “value”: “1 LCD, 1 Camera DVP 8-16-bit” }, { “label”: “Counters and Timers”, “value”: [“1 Pulse Counter, 3 Watchdog”, “4 × 54-bit general, 1 × 52-bit system”] }, { “label”: “PWM and USB”, “value”: [“LED PWM up to 8 channels, 2 MCPWM”, “1 USB OTG, 1 USB Serial/JTAG”] }, { “label”: “SDIO”, “value”: “1 Host with 2 slots” }, { “label”: “Sensors”, “value”: “Temperature, 14 Touch Sensing IOs” } ], “Wi-Fi”: [ { “label”: “Standard”, “value”: “IEEE 802.11 b/g/n-compliant” }, { “label”: “Bandwidth”, “value”: “20 MHz, 40 MHz in 2.4 GHz band” } ], “Bluetooth”: [ { “label”: “Bluetooth LE”, “value”: “Bluetooth 5, Bluetooth mesh” }, { “label”: “High Power Mode”, “value”: “20 dBm, share the same PA with Wi-Fi” } ], “Low Power Management”: [ { “label”: “Power Management Unit”, “value”: “Power Management Unit with five power modes” }, { “label”: “ULP Coprocessors”, “value”: “ULP-RISC-V coprocessor, ULP-FSM coprocessor” } ], “Security”: [ { “label”: “Features”, “value”: [“Secure Boot”, “Flash Encryption”, “AES-128/192/256, RSA, RNG, HMAC, Digital signature”] } ] }